SAT-Based Standard-Cell Layout Synthesis

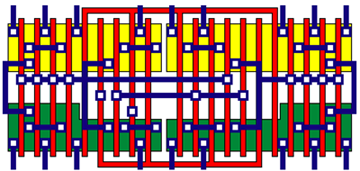

We proposed a minimum-width layout synthesis method for dual CMOS cells via Boolean Satisfiability (SAT). Cell layout synthesis problems, i.e., the transistor placement and the intra-cell routing problems are first transformed into SAT problems by this formulation. The proposed method guarantees to generate minimum-width cell layouts with routability under our layout styles.