Non-pipeline CPU using DCVSL

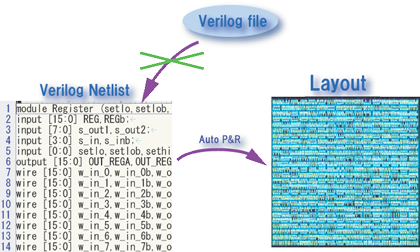

We have studied about Non-pipeline CPU using DCVSL. This CPU doesn't use pipeline architecture and doesn't supply clock to entire circuit, so it is supposed that the waveform will be relatively stable and circuit will be low power. This CPU uses asynchronous architecture therefore it needs complete-detection. To solve this problem we use DCVSL logic. DCVSL is dual-rail domino and it is suitable for complete-detection. But commercial logic synthesis tools can't use dual-rail circuit. So that we research how to convert verilog files to dual-rail verilog netlist.