Self-synchronous moebius circuit

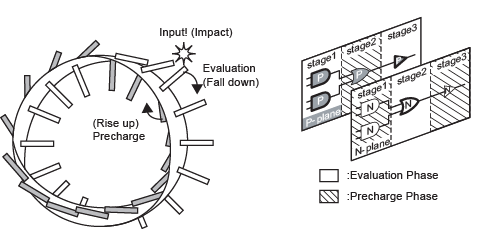

Increasing process variation in advanced process technologies demands a high timing margin for circuit designs using clock synchronous architecture, with a PVT worst case scenario that all the paths have to wait for the slowest critical path. Self-timed architecture, on the other hand, achieves high-speed operations against wide process variations since it operates with an "average" path delay. However, conventional self-timed circuits require a precharge period that cannot conduct logic operation. It is also difficult to implement fine-grained pipeline structure or wave-pipelining. By applying the structure of Moebius to a self-timed DCVSL circuit, the precharge period is concealed and a logic gate level pipeline without registers can be achieved. Also, it can detect not only permanent errors (like process defects) but also temporary errors (like soft errors). Furthermore, it can identify the gates in which the error occurred.