Process Variability Monitor for nm CMOS Process Technologies

The improvement of VLSI process technologies over the last twenty years enables us to integrate a large number of transistors on a single chip, and significantly improves the circuit performance. Instead of this steady performance improvement, however, VLSI design and verification processes have become more and more complex. Moreover, a smaller feature sizes degrade the tolerance to the PVT (Process, Voltage, and Temperature) variabilities and the reliability concerns such as negative/positive bias instability (NBTI/PBTI) have become of critical importance to nanoscale transistors.

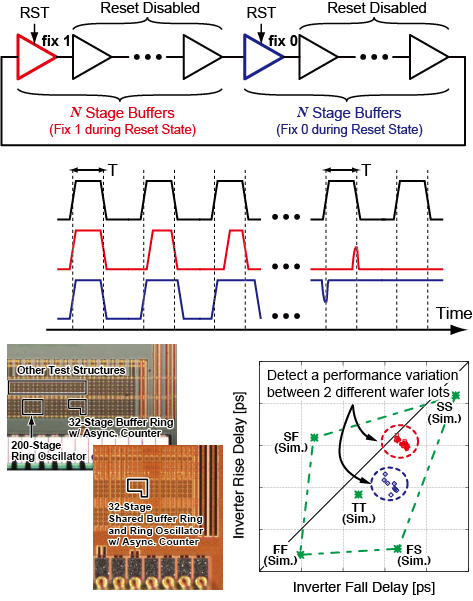

In this research, we propose an all-digital process variability monitoring circuit utilizing a simple buffer ring with a pulse counter. Our monitoring circuit counts the number of the rotations with a single pulse which propagates on the buffer ring repeatedly. This pulse vanishes after several rotations due to the difference between rise and fall delay values caused by PMOS and NMOS process variabilities. Using the proposed buffer ring circuit in combination with a simple ring oscillator circuit which monitors its oscillation period, we can calculate the rise and fall delay values and can monitor the process variabilities of PMOS and NMOS devices independently.

This technique is suitable not only for the on-chip process variability monitoring but also for the in-field monitoring of aging effects such as NBTI and PBTI, since it digitally quantifies the rise and fall delays with small area due to its simple all-digital structure.