Standard Cell Yield Optimization under Timing Constraints

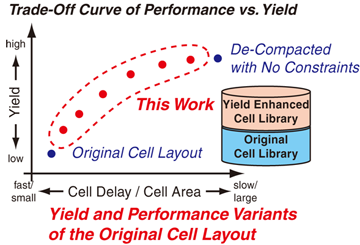

This research topic proposes a timing-aware cell layout de-compaction method for yield optimization using Linear Programming (LP). The proposed method performs a de-compaction of the original layout in order to improve the yield by minimizing the Critical Area (CA) inside the cell. This yield improvement procedure is executed under given timing constraints. To formulate the timing constraints into LP, a new accurate linear delay model which approximates the difference from the original delay is proposed.

Using the proposed timing-aware yield enhancement method, we can explore the trade-off between yield and performance, and can pick up the yield/performance variants from the trade-off curve. The effectiveness of the proposed method for OPC mask data volume reduction, redundant contact insertion, and gate layout pattern regularity enhancement is also shown.