# 回路設計技術の最新動向

名倉 徹 †, 池田 誠 ††, 浅田 邦博 †† † 東京大学工学系研究科電子工学専攻 †† 東京大学大規模集積システム設計教育研究センター (VDEC)

## 1 はじめに

携帯電話に代表されるように、電子機器の小型化が急速に進んでいる。従来はLSI設計とパッケージ・ボード設計は、ほぼ完全に分業されていたと言ってもよいであるう。しかし、さらなる小型化・高性能化のためには、相互理解が不可欠である。本発表では、現状のLSI設計フローとその問題点や最新のトピックを紹介するとともに、それらの解析・解決法がEMIの低減につながるなど、ボード設計者にとっても有用であることを示す。

## 2 回路設計フロー

#### 2.1 RTL 設計

回路動作を記述する。通常、RTL(Registor Transfer Level) とよばれる言語を用いる。あたかもプログラムを書くようなノリで設計する。

```

always @(posedge clk) begin

if (!rst)

state <= 0;

else begin

if (substrate == 0) begin

substrate <= 1;

end

if (substrate == 1) begin

:</pre>

```

#### 2.2 論理合成

論理合成とは、RTLで記述された回路をゲート (nand, nor 等) の基本ブロックに変換することである。あらかじめ、各ゲートの速度・面積・消費電力などをライブラリとして登録しておき、「速度最適化」や「消費電力最適化」などと指定すれば、それなりの回路を生成してくれる。

図1: 論理合成の結果

## 2.3 P&R, タイミング解析

P&R とは Place and Route の意味である。合成された 回路を元に、ライブラリに登録された各ゲートを隙間無 く並べ (Place)、ゲートの端子と端子を接続する (Route)。

図 2: P&R の結果

# 3 シグナルインテグリティ

数年前は RTL 設計・論理合成・P&R・タイミング解析、で完成だったが、プロセスの微細化の進行とともに、ノイズの問題が顕在化してきた。

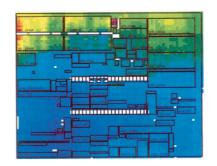

#### 3.1 電源ノイズ

トランジスタのスイッチングにより電流が発生する。電源線の寄生素子による IR ドロップおよび Ldi/dt により、電源電圧が変動する。電源線の寄生 LCR 抽出・チップ全体のスイッチング情報および電流消費を元に電源電圧変動マップを計算する [1]。

図 3: 電源電圧マップ

## 3.2 クロストークノイズ

隣り合う配線どうしの容量結合により、一方の線の電圧 変動が隣の配線にノイズを与える。特に配線間隔が100nm 程度となり、配線幅よりも配線高さの方が大きくなると、クロストークノイズの影響は深刻になる[2]。

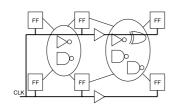

#### 3.3 クロックスキューと準同期回路

チップ面積が大きくなるにしたがって全フリップフロップに同時にクロックを配給することが困難になり、クロックスキューが生じる。設計する際には、クロックスキューを考慮したタイミング設計が必要となる。一方、回路遅延に応じたクロックスキューを意図的に挿入して高速化を図る準同期回路も提案されている[3]。

図 4: 準同期回路

#### 3.4 基板ノイズ

通常、デジタル回路のノイズがアナログ回路に影響しないように、デジタル回路用とアナログ回路用の電源線は分割する。ところが、同じ基板上に両回路があると、基板を通じてノイズが伝搬してしまう[4]。

図 5: 基板ノイズ

一方、準同期回路を応用してチップ全体でのトランジスタスイッチングを平均化し、チップの di/dt を抑えることで、基板ノイズを削減する手法も提案されている [5]。

## 4 EMI 解析 · 低減

前章では、LSI のシグナルインテグリティ向上のための施策を検討した。ここで、それらの施策がボード設計者に押し付けられている EMI 解析・削減に対して有効であることに気付く。電源ノイズ解析のためのチップレベルでの電流見積もりは、EMI 解析のための電源電流解析に流用できる。高速化のための準同期回路はスイッチングタイミングの分散化につながり、di/dt の低減、すなわち EMI ノイズ低減につながる。基板ノイズ低減のための準同期回路による di/dt は、直接 EMI 低減につながる。

## 5 di/dt 低減·測定

# **5.1** *di/dt* 測定回路

電源ノイズや EMI 解析における重要なパラメータとして、電源線の di/dt が挙げられる。電源線から発生する

磁界をスパイラルインダクタを用いて受信することにより、di/dt に比例した電圧を出力し、インダクタの値と増幅率から di/dt の値を求めることが可能である [6]。

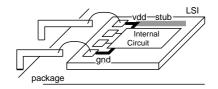

## **5.2** スタブを用いた di/dt 削減手法

スタブを LSI の電源線に直接接続することにより di/dt 電源ノイズを削減することが可能であることを示す。 HSPICE シミュレーションによると、1.8V、 $2.5 \mathrm{GHz}$  動作のテスト回路において、電源線にスタブを接続することにより、無付加・同一面積容量を接続した場合に比べてそれぞれ 48%、26% の電源ノイズを削減することが示された。また、本手法は周波数が高くなるほど効果的に働き、将来の高速化 LSI デバイスにおいて、さらに有効である [7]。

図 6: スタブを用いた電源ノイズ低減

#### 6 まとめ

LSI 設計の最新動向をまとめた。LSI 設計においてはシグナルインテグリティが問題となっており、さらに、その解析・解決手法がボード設計での EMI の解析・解決手法に応用可能であることを示した。

また、シグナルインテグリティや EMI の原因となる 電源の di/dt に関して、スパイラルインダクタを用いて di/dt を測定する方法と、スタブを用いて di/dt を低減する手法を示した。

#### 参考文献

- [1] 杉山聡、"LSI 電源配線のノイズ評価手法"東京大学大学院工学系 研究科電子工学専攻 修士論文、March 2003

- [2] "International Technology Roadmap for Semiconductors 2002 Update," [Online] Available: http://public.itrs.net/

- [3] Kazunori Inoue, et.al., "Schedule-Clock-Tree Routing forSemi-Synchronous Circuits," *IEICE Trans. Fund.*, pp.2431–2439, 1999

- [4] Makoto Nagata, et.al., "Physical Design Guides for Substrate Noise Reduction in CMOS Digital Circuits," *IEEE JSSC*, pp.539–549, 2001

- [5] Mustafa Badaroglu, et.al., "Clock Tree Optimization in Synchronous CMOS Digital Circuits for Substrate Noise Reduction Using Folding of Supply Current Transients," in *Proc. 39th Design Automation Conf.*, June 2002, pp.399–404.

- [6] Toru Nakura, et.al., "On-chip di/dt Detector Circuit for Power Supply Line," in *Proc. IEEE International Conf. on Microelectronic Test Structures (ICMTS)* 2004, to be published, March 2004.

- [7] Toru Nakura, et.al., "Theoretical Study of Stubs for Power Line Noise Reduction," in *Proc. 2003 Custom Integrated Circuit Conf. (CICC)*, Sept. 2003, 31-4.

講演者名:名倉 徹, 所属:東京大学工学系研究科電子工学専攻, 住所:113-8656 東京都文京区本郷 7-3-1, 電話:03-5841-6719, FAX:03-5841-8912, E-mail:nakura@silicon.t.u-tokyo.ac.jp