大学院輪講資料 2004 年 6 月 25 日 (金)

# CMOS イメージセンサの技術動向: CCD への再挑戦 Trend of CMOS Imaging Device Technologies

電子工学専攻 浅田研究室

博士課程 3 年 27110 大池 祐輔

#### **Abstract**

Which imaging device survives in the current fast-growing and competitive market, CCD imagers or CMOS imagers? Although this question is still argued among experts, the conclusion has not come out yet. In recent years, the power balance of CCD imagers and CMOS imagers has been changing quickly every two years. Now, CMOS image sensors challenge to take the market of CCDs again. In this paper, I introduce the state-of-the-art technologies of CMOS image sensors behind the present trend of the image sensor market.

# 1 はじめに

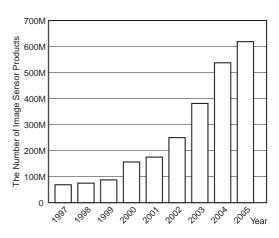

デジタルカメラや携帯電話,セキュリティ,車載用途など,近年ますます適用分野を広げるイメージセンサ (Fig.1)であるが「CCD イメージセンサ vs. CMOS イメージセンサ」の議論は未だに決着をみない、30年以上前に提案された MOS イメージセンサ [2] は,それを追うように発明された CCD イメージセンサ [3] によって一時は駆逐され,「固体撮像素子 = CCD」という時代が長く続いた.しかし,1993年にE.R. Fossumによって提案された,CMOS APS (Active Pixel Sensor)[4] の登場によって状況は大きく変わることになる.CCD イメージセンサにとって圧倒的優位であった画質の点では,回路的なアプローチから固定パターンノイズ(FPN)を抑えることに成功し,さらに,低コスト,低消費電力,ワンチップ化などの特徴が携帯電話などの要求と一致したことで,産業的にも成功したことは記憶に新しい.

一方で , 産業的に長い歴史を持つ CCD イメージセンサ の画質優位性が逆転したわけではない. CMOS イメージ センサは,回路的なアプローチに加え,プロセス技術・デ バイス技術の改善により, CCD イメージセンサに匹敵・ 凌駕する画質を現在でも追求している . そして「CCD イ メージセンサ vs. CMOS イメージセンサ」の議論の趨勢 は,2年程度の短いサイクルで変化している.カメラ付 き携帯電話の登場した 2000 年には, CMOS イメージセ ンサの需要が急激に伸びるとともに技術的な進歩も著し く, CCD イメージセンサは21世紀に生き残れるのか,と いう声すら聞こえた.しかし,2002年,デジタルカメラ や携帯電話に搭載されるイメージセンサの高解像度化が 進み,単に絵が撮れるというだけでなく,どれだけ銀塩 フィルムの写真に近いかという画質重視の風潮が, CCD イメージセンサの追い風となった. 高解像度化および低ノ イズで優位だった CCD は,その「画質のよい方式」とい う消費者のイメージも手伝って,再びCMOSイメージセ

Fig. 1. Trend of the world-wide image sensor products [1].

ンサの市場を取り返していった.当時の予測では,CCD イメージセンサの需要がその後2~3年で倍増し,CMOS イメージセンサは伸び悩むとされた.

2004年,その予測が再び揺れている.200万画素以上の 撮像センサとして,CCDイメージセンサではなく CMOS イメージセンサが市場から要求され,CCDの牙城である ハイエンド市場において,CMOSイメージセンサが競合 し始めている.本稿では,これまでの「CCD vs. CMOS」 の変遷をふまえて,CMOSイメージセンサが再び市場を 奪い返そうとする現状において,この背景にあると考え られる技術動向について紹介する.

# 2 固体撮像素子の基本原理

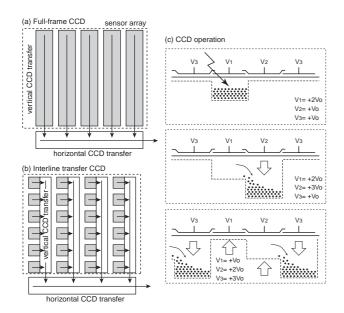

本節では, CCD イメージセンサと CMOS イメージセ ンサの基本的な差異について紹介する. CCD は 1970 年 に発明[3]されてから固体撮像素子として長い間主流で あった . Fig.2 (a),(b) に示すように , CCD イメージセンサ には主に2つの読み出し手法が利用されている.(a)のフ ルフレーム型 CCD は蓄積部と転送部が共通しており,高 い開口率を実現できるものの,転送中にも受光をしてし まうため,強い光を受光している画素を通過する列に白 い筋を引くノイズ(スミア)が発生するなどの問題がある. この方式は単純な構造から研究初期段階では適当な構造 であり,また,現在でも画素数の少ないイメージセンサ などの特定応用での応用が期待されている.一方,高解 像度化したビデオカメラには, (b) のインターフレーム型 CCD が利用されている. 蓄積部と転送部の CCD を分離 し,開口率が50%以下となるものの,電子シャッタとし ての機能を有するため,高解像度化に向いている.これ らの CCD イメージセンサは, Fig.2 (c) に示すような電荷

Fig. 2. Basic structure and operation of CCD image sensor.

Fig. 3. Passive and active CMOS image sensors.

の転送によって順次読み出しを実行し,その電荷数をほぼ失うことなく転送することが可能である.それぞれの電位の井戸の深さにはばらつきがあるが,電荷数を維持できれば最終段のアンプでは同じ条件で出力されるため,固定パターンノイズ (FPN) が原理的にないといわれている.また,現在の CCD は表面に n 層を生成することで蓄積部を基板内部に埋め込む構造となっており,基板表面で発生する暗電流を抑えることが可能である.この 2 つの特徴と開口率の高さが,CCD イメージセンサが高画質といわれる主な理由である.ただし,転送には 10 V 程度の複数の電圧を必要とし,プロセス的にも複雑であるため,消費電力やコストの点では課題を抱えている.

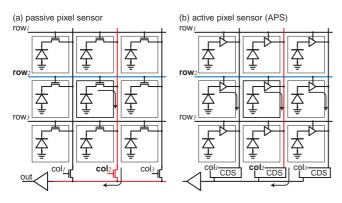

1967年に提案された MOS 型イメージセンサは,いわゆる Passive Pixel Sensor(PPS)であった. Fig.3 (a) に示すように,フォトダイオードで受光された光は光電変換により蓄積され,行および列で選択された画素の電荷を読み出す. CCD イメージセンサと異なり,任意の画素値を読み出すことができるランダムアクセスは, MOS 型イメージセンサの大きな特徴のひとつである.しかし, PPS 方式では,解像度が増加するに伴って列読み出し線および行読み出し線の寄生容量が大きくなり,読み出し感度が低くなる.また,その列ごとに異なる寄生容量によって,画質も劣化する.これらの理由から,画質の点で CCD イ

Fig. 4. Basic structures of CMOS APS.

| (a) before 200 | 1   |          | (b) after 2002 |             |          |  |  |

|----------------|-----|----------|----------------|-------------|----------|--|--|

|                | CCD | CMOS APS |                | CCD         | CMOS APS |  |  |

| Quality        | 0   | Δ        | Quality        | <b>0~</b> 0 | 0        |  |  |

| Power          | Δ   | 0        | Power          | Δ~0         | 0        |  |  |

| Cost           | 0   | 0        | Cost           | 0           | 0~0      |  |  |

| Module size    | Δ   | 0        | Module size    | Δ~0         | 0~0      |  |  |

| For movie      | 0   | Δ        | For movie      | 0           | Δ~0      |  |  |

Fig. 5. Comparison between CCD imager and CMOS imager: (a) before 2001, (b) after 2002 [5].

メージセンサに大きな差をつけられてしまい,産業的な 成功には至らなかった.

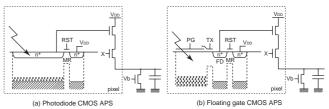

現在の CMOS イメージセンサとして実用化されている ものは, Active Pixel Sensor(APS) と呼ばれる, 画素内部 に読み出しアンプを実装されたものである、CMOS APS は 1993 年に発表され, CMOS イメージセンサが産業的 に成功するブレークスルーであった . Fig.3 (b) に示すよ うに,画素内部のアンプを介して読み出す方式は「非破 壊読み出し」と「高い読み出しゲイン」が大きな特徴と いえる. 画素構造は Fig.4(a) に示すものを基本としてお り, PN 接合フォトダイオードにて発生した電荷をソース フォロア回路を介して読み出す3トランジスタ構造であ る.また,転送ゲインを上げるために,CCD型の受光部 を採用したフォトゲート方式 (b) なども提案された.こ れらの CMOS APS は, PPS における高解像度化による寄 生容量増加の問題を解決し,画素内アンプのばらつきに 対しては,非破壊読み出しを利用した列並列相関2重サ ンプリング (CDS) 回路の提案によって解決された. 通常 の CMOS プロセスで製造可能であることは, イメージセ ンサのコストを下げ,低い単一電源での動作は,カメラ モジュールそのもののコストも下げた.1990年代末には, 暗電流や開口率の問題などにより, CCD イメージセンサ の画質にはかなわないものの,実用レベルの画質を達成 する.

## 3 「CCD vs. CMOS」競合の変遷

## 3.1 カメラ付き携帯電話の登場 (2000~2002年)

2000 年頃から,携帯電話や玩具などにイメージセンサが搭載されるようになり,CMOS イメージセンサの利点が注目された.当時の CCD イメージセンサは主に放送用ビデオカメラや,高画質が売りのデジタルカメラなどを主な市場としており,動画撮影や高画質静止画が研究開発の主たる目的であった.一方,携帯電話に要求されたカメラモジュールは,低消費電力,低コスト,小型なモジュール構成が最重要課題であった.その理由は,表

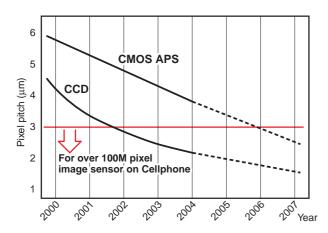

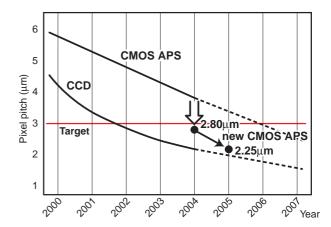

Fig. 6. Pixel pitch of CCD and CMOS APS [5, 7].

示デバイスの解像度が低かったことや, 動画撮影を要求 するまで市場が成熟していなかったことなどが挙げられ るが, 少なくとも当時の市場が要求するイメージセンサ は, CMOS APS の先天的な利点と一致していた. 当時の CMOS イメージセンサと CCD イメージセンサに対する 認識を図 5(a) に示す. 画質有利の CCD イメージセンサ は、高画質デジタルカメラや放送用機器などハイエンド 市場を中心に広がり、電力およびコスト有利の CMOS イ メージセンサは,携帯電話や光学式マウスなど画質を追 求されない市場を中心に広がった.そして,光学式マウ スが受け入れられ,さらに,カメラ付き携帯電話の爆発 的なヒットにより, CMOS イメージセンサは CCD イメー ジセンサと市場を二分する撮像素子として定着するよう になった.明確な特徴の差異により, 棲み分けがなされ 競合を起こすことは少なかったが、携帯電話の普及が急 速に加速する中 , 成熟の域に入りつつあった CCD イメー ジセンサと比較して,研究開発が盛んにされる CMOS イ メージセンサに注目が集まり「CCD イメージセンサは21 世紀に生き残れるか?」という議論すらあった.

#### 3.2 高解像度化による画質の追求 (2002~2004年)

2002 年頃から,30 万画素を超えるイメージセンサが 携帯電話に搭載され,100 万画素も視野に入ってくると, 携帯電話のイメージセンサが単なるオマケ要素ではなく, 「カメラ」としての画質を要求されるようになる.また, 限られたモジュールサイズで高い解像度を実現するには, 小さな光学寸法に多くの画素を実装する,すなわち,画 素ピッチを縮小する必要がある.つまり,

- 美しい画質

- 小さな画素ピッチ

の2点が,携帯電話搭載用のイメージセンサにも強く求められることになった.このような背景から,この2つの条件を満たしていたCCDイメージセンサが,カメラ付き携帯電話市場をCMOSイメージセンサから奪うことになる.

2002 年頃の CCD イメージセンサおよび CMOS イメージセンサの位置づけは,2000 年当初とは異なり Fig.5 (b) のように,その境界があいまいになっていた.CCD イメー

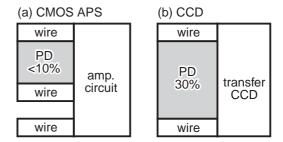

Fig. 7. 2.8  $\mu$ m-pitch pixel layout: (a) CMOS APS, (b) CCD.

ジセンサは低消費電力化と周辺回路のワンチップ化を押し進めた.たとえば,フルフレーム方式の問題であったスミア雑音などを画像演算処理によって除去する技術を考案することで,12 V - 15 V の水平転送を不要とし,7 V - 8 V 程度の垂直転送のみで高画質撮影を可能とした[6].中耐圧プロセスでの製造が可能となり,デジタル回路などの集積も容易としている.このような技術により,CCDイメージセンサは消費電力およびコストの点で,CMOSイメージセンサに近づいていた.一方,CMOSイメージセンサは高画質化を狙った埋め込みフォトダイオードの採用などで,画質改善を図った.一方で,プロセスが複雑化しコストが高まっていた.こうした棲み分けの境界があいまいとなることで,両者の関係は競合へと変化した.

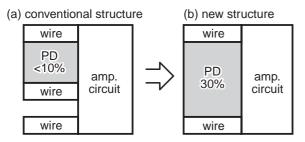

2000 年以降の CMOS イメージセンサおよび CCD イ メージセンサの画素ピッチの変遷を Fig.6 に示す.携帯電 話への 100 万画素イメージセンサ搭載が実現する 2003 年 前後では,携帯電話機に搭載可能なモジュールは「高さ 7 mm 台, 光学寸法 1/4」が上限といわれていた [7]. そ こから試算すると,100万~130万画素を実現するには画 素ピッチが  $3 \mu m$  以下でなければならない.一方,画素 ピッチを小さくするには,単に製造プロセスを微細化さ せればいいというだけではない.画素寸法が小さくなる と受光量が減少し,画質が劣化する.単位面積当たりの 感度向上が欠かせず、各メーカーの技術力が最も問われ る部分であるが,その構造上の点から,Fig.6 に示すよう に CCD イメージセンサの方がピッチの縮小が早かった. Fig.7(a) に示すように,埋め込みフォトダイオードを用い た CMOS APS の画素回路は横方向に 3 本の配線とアンプ 回路が必要である.このため,画素ピッチを縮小し,2.8 μm 程度に達すると, 受光部の開口率は 10% 以下となって しまう . CCD イメージセンサは構造がより単純であるた め, 2.8 μm ピッチにおいても 30% 程度の開口率を実現で きる.このような理由から,2002年から2003年にかけ て,100万画素を超える携帯電話のイメージセンサの選択 肢から CMOS イメージセンサが姿を消すことになった.

## 4 画素ピッチの予測と実際

前節における「CCD vs. CMOS」の変遷をみると、2004年以降の競合のキーは、画素ピッチの縮小による高解像度化と、トレードオフにある感度や S/N といった画質の改善であるといえる。もちろん高解像度化を実現するために、従来から画素ピッチの縮小は取り組まれていた。ここにきて、それが決定的な課題とされるのには、従来の

|                                        |      |      |      |      |      |      |      | futur          | e prosp         | ects            |                |

|----------------------------------------|------|------|------|------|------|------|------|----------------|-----------------|-----------------|----------------|

|                                        | 1980 | 1983 | 1986 | 1989 | 1992 | 1995 | 1998 | 2001           | 2004            | 2007            | 2010           |

| Minumum lithographic feature size (μm) | 2    | 1.5  | 1.0  | 0.7  | 0.5  | 0.35 | 0.25 | 0.18           | 0.13            | 0.1             | 0.07           |

| CMOS imager pixel size (µm)            | 40   | 28   | 20   | 14   | 10   | 7    | 5    | <b>5</b> (3.5) | <b>5</b> (2.45) | <b>5</b> (1.72) | <b>5</b> (1.2) |

| Fill factor (%)                        | 25   | 25   | 25   | 25   | 25   | 25   | 25   | 53<br>(25)     | 82<br>(25)      | 91<br>(25)      | 96<br>(25)     |

Fig. 8. Future prospects at 1996 [8].

取り組みでは限界に至ったからである.2004年現在における画素ピッチの推移と予測は Fig.6 に示した通りであるが,1996年と2000年,それぞれの時点における画素ピッチ縮小の限界における予測は興味深い [8,9].

## 4.1 1996 年時点での画素ピッチ縮小に対する見解

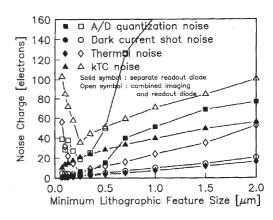

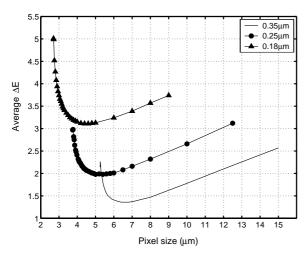

1996 年時点での画素ピッチ縮小に対する検討 [8] では,有名な「Moore の法則」[10] にもとづくプロセステクノロジーの変遷と,1996 年以降の予測について論じている. Fig.8 はその予測の一部であるが,興味深いのは CMOSイメージセンサの画素ピッチはプロセステクノロジーの変遷に従って縮小してきたが,2001 年を境に  $5~\mu m$  ピッチで限界に達すると結論している.ここでは,その理由のひとつとしてレンズの回折限界を挙げているが,光電変換ゲインや S/N などの側面からの検討により, $0.25~\mu m$ プロセス以降では,CMOS イメージセンサのトレンドが標準 CMOS テクノロジーから離れていくだろうと述べている. Fig.9 はノイズレベルに関する検討結果である.

## 4.2 2000 年時点での画素ピッチ縮小に対する見解

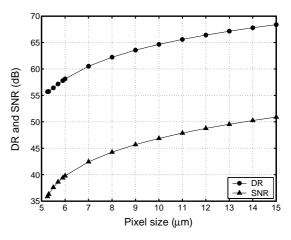

2000 年時での画素ピッチ縮小に対する検討 [9] では,簡単なモデル式からダイナミックレンジ (DR) と SN 比 (SNR) の画素サイズに対する傾向を見積もっている.ダイナミックレンジは以下の式で表現できる.

$$DR = 20 \log_{10} \frac{i_{max}}{i_{min}}$$

$$= 20 \log_{10} \frac{q_{max} - i_{dc}t_{int}}{\sqrt{\sigma_r^2 + q_{idc}t_{int}}}$$

(1)

ここで  $i_{max}$  は飽和しない電流信号の最大値 ,  $i_{min}$  は検出可能な最小値である . また , q は電子の電荷量 ,  $i_{dc}$  は暗電流 ,  $t_{int}$  は蓄積時間 ,  $\sigma_r^2$  は kTC ノイズ (リセットノイズ) が支配的なノイズ成分である . また , SN 比は光電流  $i_{ph}$  の関数として以下の式で表現される .

$$SNR(i_{ph}) = 20 \log_{10} \frac{i_{ph}t_{int}}{\sqrt{\sigma_r^2 + q(i_{ph} + i_{dc})t_{int}}}$$

(2)

支配的なノイズ成分として,リセットノイズ,光ショットノイズ,暗電流ショットノイズを考慮している.これらのモデル式導出は [11] に詳しい.Fig.10 に画素サイズとダイナミックレンジおよび SN 比の関係を示す.最大電荷量  $q_{max}$  は受光部容量 C と電圧振幅  $V_s$  の積であり,画素

Fig. 9. Input referred noise charges as a function of the minimum feature size [8].

Fig. 10. Dynamic range and signal-to-noise ratio as a function of pixel size [9].

は出 サイズの縮小に比例して C と kTC が減少することから , は暗 ダイナミックレンジが劣化する . また , 画素サイズの減 少により光電流 iph が減少し , SN 比も劣化することがわ かる . リセットノイズは CDS 回路によってほぼ完全に取 り除けることが知られているが , ショットノイズに関して は電子/光子の物理的揺らぎであるため不可避である . こ れらは入力量子数の平方根に比例して確率的に揺らぐた め , 入射光の増加と 1 画素あたりの取り扱い光量子の数 を増やすことが画質向上には欠かせない . これが画素サイズをむやみに小さくできない大きな理由となっている .

Fig.11 は各プロセステクノロジーにおける画素サイズと画質の評価である.ここではカメラシミュレータと S-CIELAB[12] を用いて得られた画像と,完全な

Fig. 11. Average  $\Delta E$  versus pixel size as technology scales (estimated at 2000) [9].

Fig. 12. Buried photodiode structure with a transfer gate and a floating diffusion region [13].

CSF(Contrast Sensitivity Function) 画像との比較によるノイズ評価基準  $\Delta E$  を示している。  $\Delta E$  が小さいほど画質がよいといえる。この評価では,チップサイズを一定とし、画素サイズが縮小することで解像度が上がると仮定している。この結果から,現状の標準 CMOS プロセスによる CMOS イメージセンサでは, $0.25~\mu m$  プロセス以降では急激に画質が劣化するという 1996 年当初と同じ結果が得られている。また,画素サイズに関しても,プロセス微細化が進んでも $5~\mu m$  ピッチ程度が限界であるという結論に至っていた。

## 5 CMOSイメージセンサの画素小型化技術

2004年現在,当時の予測に反して画素の小型化が進んでいる.これは,予測が完全に外れたわけではなく,ひとつは  $0.25~\mu m$  以降は標準 CMOS プロセスから脱却する必要があるという示唆に従ったためといえる.Fig.6 に示したように,携帯電話搭載に向けた  $100~ \rm T$  画素以上のデバイス ( $3~\mu m$  ピッチ以下)を実現できなかった CMOS イメージセンサであるが, $2003~ \rm 4~\mu m$  に近づいている.本節では,現在の標準 CMOS プロセスから脱却した受光部の改善による高画質化の技術 [13]—[17] を簡単に紹介する.さらに, $2004~ \rm 4~\mu m$  前後の CMOS イメージセンサ [18]—[20] が相次いで発表され,画素ピッチの推移 (Fig.6)を大きく加速した.これにより, $2004~ \rm 4~\mu m$  の

Fig. 13. Sensing scheme and photodiode structure of X3 [14].

Fig. 14. VMIS pixel structure [16].

「CCD vs. CMOS」の行方が再び CMOS イメージセンサ優位へと傾いている. これらの CMOS イメージセンサの最新技術を紹介する.

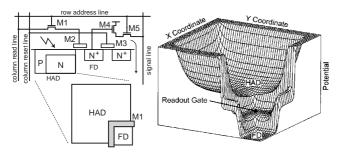

#### 5.1 標準 CMOS プロセスからの脱却

前述のように標準 CMOS プロセスによる高解像度化・ 高画質化の限界は指摘されており, それに従い2000年頃 から脱標準 CMOS プロセスの "CMOS イメージセンサ" が開発された.現在のCMOSイメージセンサで広く使わ れている受光構造は,埋め込みフォトダイオードによるも の [13] である . Fig.4(b) のフォトゲート型 CMOS APS と 同様に,電荷転送による高い変換ゲインを実現でき,フォ トゲート型 CMOS APS における薄膜ゲート電極の形成プ ロセスや、その電極による光の吸収の問題を解決してい る.また,CCD 同様に受光部が基板表面に出ていないた め,結晶欠陥で発生する暗電流を低く抑えることができ, 高い S/N 比も実現している.これにより 2002 年以降,現 在までの CMOS イメージセンサは,高い画質を実現しな がら画素ピッチを  $4 \mu m$  まで縮小することができた.この ようにして, CMOS イメージセンサは CCD イメージセ ンサに匹敵する画質を実現するとまでいわれはじめたが, Fig.5(b) に示したように,画質向上のためにプロセスコス トを犠牲にしてきたといえる.

埋め込み PD の採用が CMOS イメージセンサに CCD の要素を取り入れたアプローチであるのに対し, CCD と

Fig. 15. 2.8  $\mu$ m-pitch pixel layout: (a) the conventional structure (see Fig.7(a)), (b) a new structure.

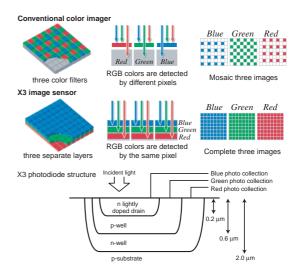

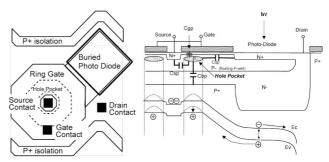

は異なる斬新なアプローチで高画質・画素ピッチ縮小を 図った CMOS イメージセンサとして, X3 方式 [14, 15] や VMIS 方式 [16, 17] とよばれる CMOS イメージセンサが ある . X3 方式は Fig.13 に示すように , 深さ方向に 3 層の 受光部を形成し, 光の侵入長が波長によって異なるとい う減少を利用して RGB 色情報を 1 画素で取得すること ができる、これによりカラーフィルタを不要とし、偽色 のないシャープな画像を得ることができる.また,従来 の3あるいは4画素に相当する情報を1画素で取得でき るため、実効的な解像度を高くすることができる.VMIS 方式は , Fig.14 に示すような埋め込みフォトダイオード とひとつのトランジスタでリセット,選択,読み出しの 動作を実行できる方式である、リングゲート直下に高濃 度の p+領域 (Hole Pocket) を形成し, 蓄積されたホール の量に応じて変化する閾値を読み取ることで画像を得る。 数種類の制御電圧信号が必要だが,20%の開口率を有す る 4.2 μm ピッチの画素を実現している.また,リセット トランジスタの寄生容量やクロストークノイズが無視で きるなど,画質の点でも利点を有している.この2方式 は2002年に相次いで発表され,現在では実用化に至って いる.

#### 回路共有による画素ピッチ縮小技術

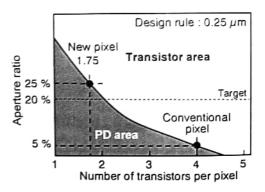

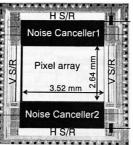

標準 CMOS プロセスからの脱却により,暗電流の低減 が実現され、物理的に不可避なショットノイズが画質を 決める主要因となってきた.これにより,充分な開口面 積を確保できる場合は CCD に匹敵する画質を実現可能と なったが, 3 μm 前後の画素ピッチにおいては, Fig.7 に 示したように, 開口率の減少によるショットノイズ増加 の問題が残っていた.2004年4月, Canon, 松下電器産 業(以下,松下), Sonyの3社はそれぞれ,埋め込みフォ トダイオードによる電荷完全転送を利用した読み出しア ンプの共有技術と、プロセスの高さ方向の最適化などに よって画素ピッチ縮小のブレークスルーを発表した、こ れらの技術は, Fig.15 に示すように, 受光部面積の占有 率を上げることに成功し, 2.8 μm 画素ピッチにおいても 30% 前後の開口率を実現, CCD に匹敵する画質を提供可 能とした.

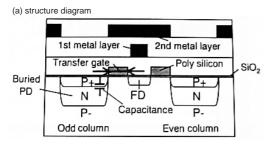

Fig.16 は松下の発表した「vMAICOVICON」[19] の画 素構造である、前述した通り、主な CMOS イメージセン サは標準 CMOS プロセスのまま製造されることは少なく,

Fig. 16. Pixel structure [19, 21].

Fig. 17. Fill factor as a function of the number of transistors per pixel [19, 21].

在では, CMOS イメージセンサは標準 CMOS プロセスの イメージセンサという意味ではなく,電荷を各画素内の MOS トランジスタ・アンプを用いて増幅し, XY アドレ スで外部へ読み出す方式のイメージセンサを指すように なっている.一方で,各社はそれらのイメージセンサを別 名で表現することが多い、松下の「vMAICOVICON」や 東芝の「Dynastron」などがその例である.読み出し方式 に注目した現在の解釈では CMOS イメージセンサそのも のであるが,各社が名称を変えるのには「CMOSイメー ジセンサは画質が良くない」という消費者の旧来からの 印象を配慮しているためである. 本稿では, 読み出し方 式をもって CCD イメージセンサと CMOS イメージセン サに分類している.

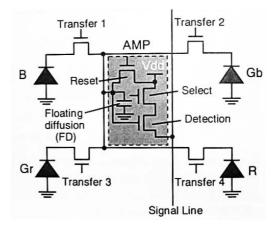

Fig.16 は,4 画素で信号検出アンプ回路を共有してい る.信号検出アンプは FD 部と3個のトランジスタから 構成で構成される.このため,4画素を1ユニットとして 合計7個のトランジスタで構成されており,1画素あたり 1.75 トランジスタとなっている . [19] では ,  $0.25~\mu {

m m}$  プ ロセスを用いて 2.25 μm 画素ピッチ, 開口率 25% という CCD イメージセンサに匹敵する画素サイズと開口率を達 成している (Fig.6, Fig.7, Fig.15 参照) . Fig.17 は , 2.25µm 画素ピッチにどれだけの開口率が確保できるか、画素内 のトランジスタ数に対して見積もった結果である. 従来 構成では、1 画素あたり4トランジスタ必要となり,開口 率は 5% 程度となってしまう. アンプ回路の共有構造は, なんらかのカスタマイズが加えられている .そのため ,現 25%の開口率を実現し ,CCD に匹敵する画質を実現可能

Fig. 18. Readout operation diagram [19, 21].

Fig. 19. Device structure [19, 21].

## Gate driving voltage 2.5 V

Fig. 20. Potential diagram of a readout part [19, 21].

# とする.

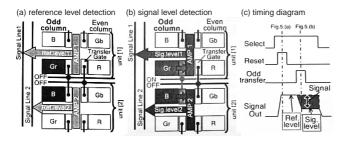

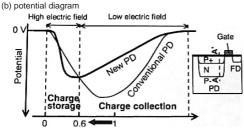

Fig.18 に,4 画素共有型構造の動作図を示す.転送ゲートが OFF の状態でリセットし,リセット時の出力信号を参照レベルとして CDS 回路で保持する.転送ゲートを ON にすると,蓄積電荷が FD へ完全転送され,信号レベルを出力する.設計上の理由と考えられるが,行選択線は上下2ユニットの隣接画素で共有している.Fig.19 に受光部の構造とポテンシャル図を示す.2.5 V の低電圧動作で電荷完全転送を行なう工夫として,

- 非対称電界フォトダイオード構造

- 短ゲート長フォトダイオード電荷読み出し構造

を提案している.電荷蓄積領域を従来の60%の深さとすることで,低電圧でも高密度に電荷を蓄積でき,広ダイナミックレンジを実現する高電界領域を設けている.また,フォトダイオード深部を $P^-$ とすることで,フォトダ

(a) chip microphotograph

(b) sample image

Fig. 21. Chip microphotograph and sample image [19, 21].

Table 1. Chip specifications [19]. Pixel size  $2.25 \,\mu \text{m} \times 2.25 \,\mu \text{m}$ Optical format 1/4 inch The number of pixels  $1616 (H) \times 1217 (V) = 2 M$ Transistors per pixel 1.75 Fill factor 25 % Saturation 5000 electrons 3800 electrons/lx·s Sensitivity Frame rate 15 frames/s Image lag No image lag Power supply voltage 2.5 V

Fig. 22. Leading-edge trend of pixel pitch of CCD and CMOS APS.

イオード深部分で発生する電荷を効率よく集め,高感度を実現できる低電界領域も設けている.さらに,Fig.20に示すように,読み出しゲート長を従来の60%短縮することで,FDに印可された電圧のフリンジング電圧がフォトダイオードに到達し,残像を完全に無くすことができる.

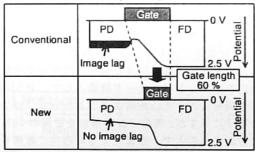

Fig.21 に試作されたイメージセンサと撮像例を示す. 本センサは, 1/4 型光学サイズの撮像領域 ( $3520~\mu m \times 2640~\mu m$ ) に 200 万画素を集積している. センサ仕様を Table 1にまとめる.

## 6 現在の「CCD vs. CMOS」

CCD および CMOS イメージセンサの画素ピッチの変遷 (Fig.6) に最新の CMOS イメージセンサ技術を加味すると, Fig.6 のようになる. 前節で紹介した技術による 2.25  $\mu$ m 画素ピッチのイメージセンサ量産は 2004 年末になる見込みだが, 同技術による 2.80  $\mu$ m 画素ピッチの製品は量産が始まっている. 2004 年以降, CMOS イメージセン

| Table 2  | Comparison | among the la  | est and sched | uled products | of CCD and  | CMOS imagers        | [7]    |

|----------|------------|---------------|---------------|---------------|-------------|---------------------|--------|

| 1ainc 2. | Comparison | annone uic ia | est and sched | aica moducis  | OI CALL AIR | i Cavicas iiliageis | 1 / 1. |

|               | Types | Pixel reso. | Pixel pitch           | Min. lux.      | Power                    | Commercial production |

|---------------|-------|-------------|-----------------------|----------------|--------------------------|-----------------------|

| Matsushita    | CMOS  | 2 M         | $2.8 \mu\mathrm{m}$   | 5 lx (7.5 fps) | 2.9 V                    | Mar. 2004             |

| Sony          | CMOS  | 2 M         | $2.9 \mu m$           | 5 lx (15 fps)  | 2.7/1.8 V                | 3rd Qtr of 2004       |

| Toshiba       | CMOS  | 1.3 M       | $3.3 \mu m$           | 5 lx           | 2.8/1.5 V                | 2nd Qtr of 2004       |

| Renesas Tech. | CMOS  | 1.3 M       | $3.8 \mu\mathrm{m}$   | _              | 2.85/1.85 V              | 3rd Qtr of 2004       |

| Micron Tech.  | CMOS  | 1.3 M       | $3.6 \mu\mathrm{m}$   | 3 lx           | $2.5 \sim 3.1 \text{ V}$ | Now available         |

| Sony          | CCD   | 1.3 M       | $3.125  \mu \text{m}$ | 5 lx (15 fps)  | 12.5/5/3/-6.5 V          | Mar. 2003             |

| Sharp         | CCD   | 2 M         | $3.2 \mu\mathrm{m}$   | 2 lx (5 fps)   | $15 \sim -8 \text{ V}$   | Dec. 2003             |

| Sanyo         | CCD   | 1 M         | $2.7 \mu m$           | _              | 2.9 V                    | Aug. 2004             |

| Fuji Film     | CCD   | 1 M         | _                     | 2 lx           | $3.2 \sim 5.5 \text{ V}$ | Oct. 2003             |

サが画質/解像度の点でも猛追することが予想され,カメ ラ付き携帯電話のマーケットからは,既に200万~300 万画素の CMOS イメージセンサの要求がメーカーに殺到 しているという [22]. Table 2 に, 現在量産, あるいは量 産予定である各社の CMOS および CCD イメージセンサ の仕様の一部をまとめた.画質などは最小被写体照度だ けで評価されるものではなく,また,各イメージセンサ の性能を一般化することは困難である.しかし,100万 画素では一歩遅れをとった CMOS イメージセンサである が,年内に予定されている高解像度CMOSイメージセン サは,フレームレートを加味すると CCD イメージセン サとほぼ同等の画質が期待できるといえる.さらに,従 来からの特徴である低電圧電源動作や,コストの面で未 だ CCD イメージセンサに利点を維持している CMOS イ メージセンサが,今後の高解像度カメラ付き携帯電話か らデジタルカメラといったハイエンド市場にて CCD と競 合するのは間違いないと考えられる.

## 7 まとめ

本輪講では,議論され続ける一方で,目まぐるしく予測 と結果が変わる「CCD イメージセンサ vs. CMOS イメー ジセンサ」のこれまでの変遷をまとめ,現在の状況と最 新技術動向について紹介した. CMOS イメージセンサが 再び CCD イメージセンサの市場を脅かす理由を検討し, 2004 年以降の 1~2 年は CMOS イメージセンサに注目が 再び集まると考えられる.今回は主にCMOSイメージセ ンサ側から検討をしたが, CCD イメージセンサも CMOS イメージセンサの利点を取り込むべく, 低電源供給への 取り組みなどが消費電力低減などを実現している.一方 で,CCDに匹敵する画質を実現することで,次世代の市 場といわれる車載用途など、高機能化を要求する応用と 親和性の高い CMOS イメージセンサが大きく躍進する可 能性は高い.双方の技術向上が互いの予測を裏切り,そ れにより進歩してきたイメージセンサは,今後もCCDと CMOS イメージセンサの競合によって新しい価値を生み 出していくと考えられる.

## 参考文献

- [1] 日経エレクトロニクス 2003 年 2 月号, No. 840, 日経 BP 社.

- [2] G. P. Weckler, "Operation of p-n junction photodetectors in a photon flux integration mode," *IEEE J. Solid-State Circuits*, vol. SC–2, pp. 65–73, 1967.

- [3] W. S. Boyle and G. E. Smith, "Charge-coupled semiconductor devices," *Bell Systems Technical Journal*, vol. 49, pp. 587–593, 1970

- [4] E. R. Fossum, "Active Pixel Sensors: Are CCD's Dinosaurs?," in *Proc. SPIE*, vol. 1900, pp. 2–14, 1993.

- [5] 日経マイクロデバイス 2003 年 1 月号, No. 211, 日経 BP 社.

- [6] SANYO NewRelease, Feb. 7, 2001 (http://www.sanyo.co.jp/koho/hypertext4/0102news-j/0207-2.html)

- [7] 日経エレクトロニクス 2004年4月号, No. 226, 日経 BP 社.

- [8] H. S. Wong, "Technology and Device Scaling Considerations for CMOS Imagers," *IEEE Trans. Electron Devices*, vol. 43, no. 12, 1996

- [9] T. Chen, P. Catrysse, A. E. Gamal, and B. Wandell, "How Small Should Pixel Size Be?" in *Proc. SPIE*, vol. 3965, pp. 451–459, 2000.

- [10] G. E. Moore, "Cramming More Components Onto Integrated Circuits," *Electronics*, vol. 38, no. 8, pp. 114–117, 1965.

- [11] D. X. Yang and A. E. Gamal, "Comparative Analysis of SNR for Image Sensors with Enhanced Dynamic Range," in *Proc. SPIE*, vol. 3649, pp. 197–211, 1999.

- [12] Z. Zhang and B. A. Wandell, "A Spatial Extension of CIELAB for Digital Color Image Reproduction," Society for Information Display Symposium Technical Digest, vol. 27, pp. 731–734, 1996.

- [13] K. Yonemoto and H. Sumi, "A CMOS Image Sensor with a Simple Fixed-Pattern-Noise-Reduction Technology and a Hole Accumulation Diode," *IEEE J. Solid-State Circuits*, vol. 35. no. 12, 2000.

- [14] Foveon Inc., http://www.foveon.com/

- [15] United States Patent 5,965,875

- [16] T. Miida, K. Kawajiri, H. Terakago, T. Endo, T. Okazaki, S. Yamamoto, and A. Nishimura, "A 1.5M Pixel Imager with Localized Hole-Modulation Method," *IEEE ISSCC Dig. of Tech. Papers*, pp. 42–43, 2002.

- [17] United States Patent 6,051,857

- [18] H. Takahashi, M. Kinoshita, K. Morita, T. Shirai, T. Sato, T. Kimura, H. Yuzurihara, and S. Inoue, "A 3.9μm Pixel Pitch VGA Format 10b Digital Image Sensor with 1.5-Transistor/Pixel," *IEEE ISSCC Dig. of Tech. Papers*, pp. 108– 109, 2004.

- [19] M. Mori, M. Katsuno, S. Kasuga, T. Murata, and T. Yamaguchi, "A 1/4in 2M Pixel CMOS Image Sensor with 1.75 Transistor/Pixel," *IEEE ISSCC Dig. of Tech. Papers*, pp. 110–111, 2004.

- [20] K. Mabuchi, N. Nakamura, E. Funatsu, T. Abe, T. Umeda, T. Hoshino, R. Suzuki, and H. Sumi, "CMOS Image Sensor Using a Floating Diffusion Driving Buried Photodiode," *IEEE ISSCC Dig. of Tech. Papers*, pp. 112–113, 2004.

- [21] 春日 繁孝, 森 三佳, 勝野 元成, 村田 隆彦, 山口 琢己, "1.75 トランジスタ画素構成による 1/4 型 200 万画素 CMOS イ メージセンサ," 映像情報メディア学会技術報告, vol. 28, no. 23, pp. 31 – 34, 2004.

- [22] 日経マイクロデバイス 2004年3月号, No. 225, 日経 BP 社.