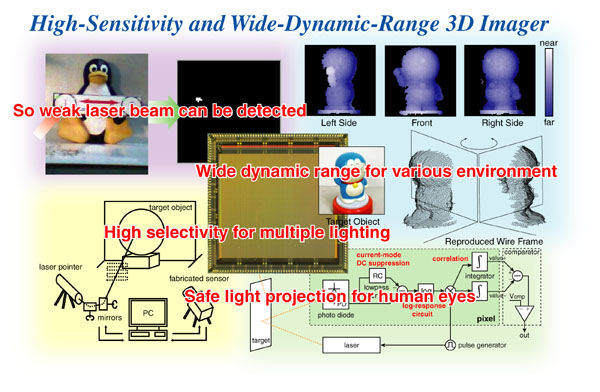

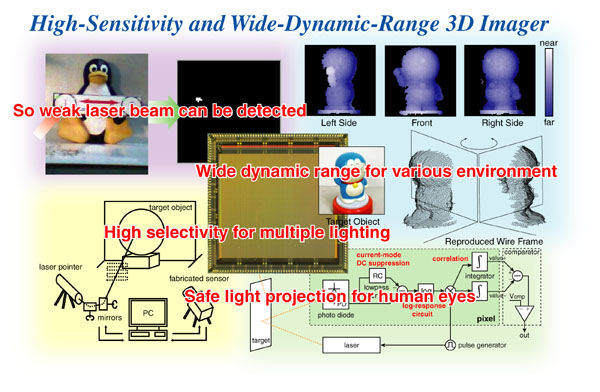

光切断法を用いた3次元計測システムは、非常に高い精度の3次元形状を得ることが可能ですが、

屋外など強い光が外乱として存在すると強いレーザ光投射が必要となり実用的でありませんでした。

私たちは、ダイナミックレンジの広い対数型の受光部と高いS/Nで選択的に光を取得できる

検波方式を効果的に融合したイメージセンサを開発しました。

これにより、外乱光の1/100程度の微弱なレーザ光投射を飽和することなく

検知することが可能となります。

本成果は集積回路最高峰の会議とされるISSCC 2003にて発表しました。

Y. Oike, M. Ikeda, and K. Asada,

``A 120 x 110 Position Sensor With the Capability of Sensitive and

Selective Light Detection in Wide Dynamic Range for Robust Range Finding,''

IEEE Journal of Solid-State Circuits,

Vol. 39, No. 1, pp. 246 -- 251, Jan. 2004.

[PDF]

(This achievement was partly presented in

IEEE Int. Conf. Solid-State Circuits (ISSCC), Feb. 2003.

[PDF])

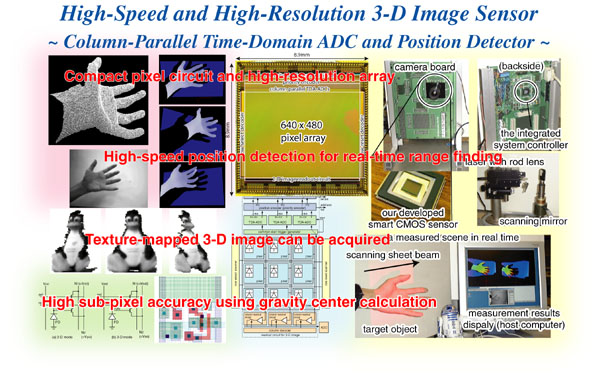

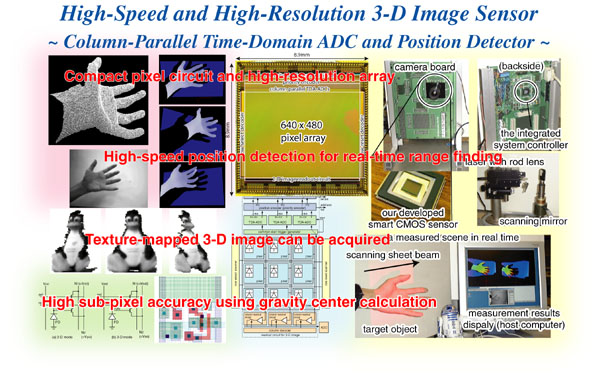

高精細・実時間3次元イメージセンサの実現には、通常のイメージセンサの

3桁高速な画像の取得が必要です。私たちは、距離計測に必要な情報が

投射したレーザ光の位置情報であることに注目し、

新しいアクセス手法を適応閾値回路と時間領域近似AD変換を用いて

実現しました。

これまで実現されていなかった、640x480画素(VGA)や1024x768画素(XGA)の

距離画像を実時間かつ1ミリを切る高精度で取得することを可能とします。

本成果は集積回路に関する3大会議のひとつとされる

VLSIシンポジウム 2003にて発表しました。

Y. Oike, M. Ikeda, and K. Asada,

``Design and Implementation of Real-Time 3-D Image Sensor

With 640 x 480 Pixel Resolution,''

IEEE Journal of Solid-State Circuits,

Vol. 39, No. 4, pp. 622 -- 628, Apr. 2004.

[PDF]

(This achievement was partly presented in

IEEE Symposium on VLSI Circuits (Symp. VLSI), Jun. 2003.

[PDF])

Y. Oike, M. Ikeda, and K. Asada,

``A High-Speed XGA 3-D Image Sensor and Its Applications,''

in Proc. of the 6th Biannual World Automation Congress (WAC 2004),

Jun. 2004.

[PDF]

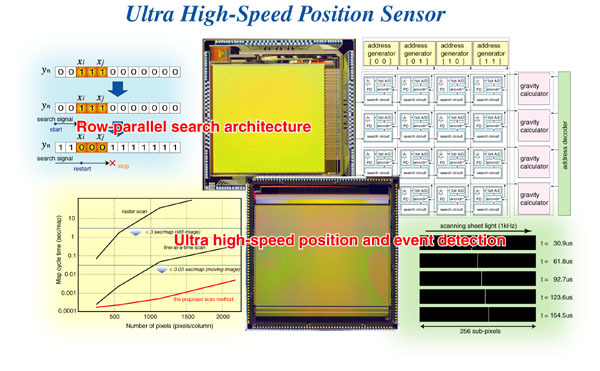

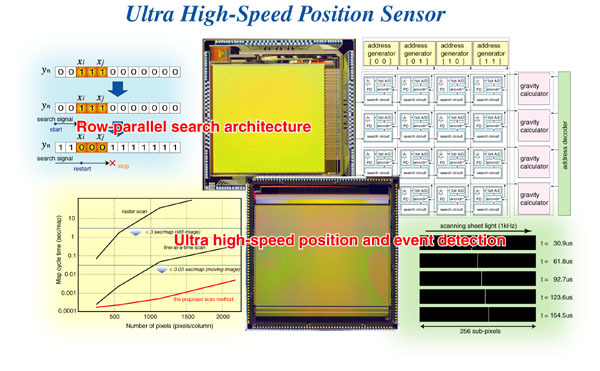

私たちの提案する「スマートアクセス」は、センサ面上に

点在する「有意な情報」を効果的に取得するセンサアーキテクチャです。

ここでは、高精度3次元計測におけるセンサ面上での投射光位置検出を

列並列探索信号伝搬アクセス技術を用いて高速に実行します。

1フレーム内での複数回アクセスが可能となり、

輝度分布の取得などさらなる高精度化が図れます。

本提案は、回路システムに関する最大規模の国際会議であるISCASにて

2003年に発表しました。

また、この技術を発展させ375x365画素の3次元イメージセンサとして

実装し、1000枚/秒を超える距離計測システムの実現を目指しています。

最新の成果は、集積回路最高峰の会議とされるISSCC 2004にて発表しました。

Y. Oike, M. Ikeda, and K. Asada,

``A 375 x 365 High-Speed 3-D Range-Finding Image Sensor

Using Row-Parallel Search Architecture and Multi-Sampling Technique,''

IEEE Journal of Solid-State Circuits,

Vol. 40, No. 2, pp. 444 -- 453, Feb. 2005.

[PDF]

(This achievement was partly presented in

IEEE Int. Conf. Solid-State Circuits (ISSCC), Feb. 2004.

[PDF])

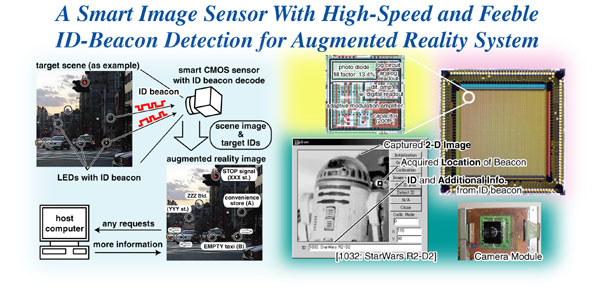

実世界の情報とコンピュータ世界の情報を効果的に融合し、

その情報をユーザに提供する拡張現実システムのひとつとして、

発光デバイスを用いたシステムが提案されています。

これまで、通常のイメージセンサでは

30枚/秒の拡張現実画像にせいぜい数bitの情報しか

付加できませんでした。

私たちは、画素内に輝度変化を検知しデジタル信号として

読み出すことができるイメージセンサを提案し、

より高速なビーコン検出とともに微弱な光信号を

外乱内から取得する試みを進めています。

本研究成果はISSCCのヨーロッパ版である

ESSCIRC 2003にて発表しました。

Y. Oike, M. Ikeda, and K. Asada,

``A Smart Image Sensor With High-Speed Feeble ID-Beacon Detection

for Augmented Reality System,''

in Proc. of IEEE European Solid-State Circuits Conference (ESSCIRC),

pp.125 - 128, Sep. 2003.

[PDF]

私たちの開発した実時間・高精細3次元イメージセンサの性能を

引き出すには、センサ制御、データ伝送、信号処理などの

ハードウェア/ソフトウェア開発が必要不可欠です。

私たちはFPGAを用いた制御系の開発と、SCSIインターフェースの

実装によって3次元撮像カメラを構築し、

さらに演算・描画ソフトウェアを開発しました。

これにより、実際に動いている物体の3次元形状に対して、

1ミリ以下の高精度かつ640x480距離データという高密度での

実時間取得に成功しました。

本成果はセンサに関する多くの研究者が集まるIEEE SENSORSにて

2003年に発表しました。

Y. Oike, H. Shintaku, S. Takayama, M. Ikeda, and K. Asada,

``Real-Time and High-Resolution 3-D Imaging System Using Light-Section Method

and Smart CMOS Sensor,''

in Proc. of IEEE International Conference on Sensors (IEEE SENSORS),

pp.502 - 507, Oct. 2003.

[PDF]

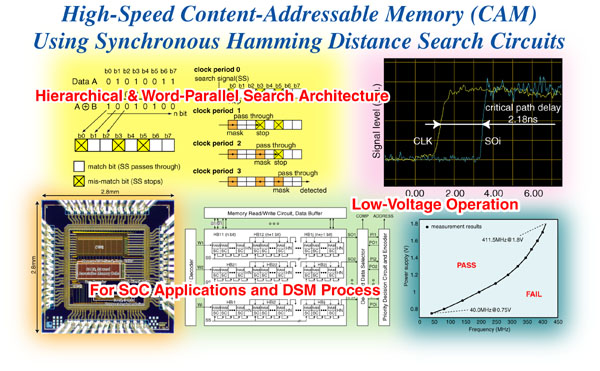

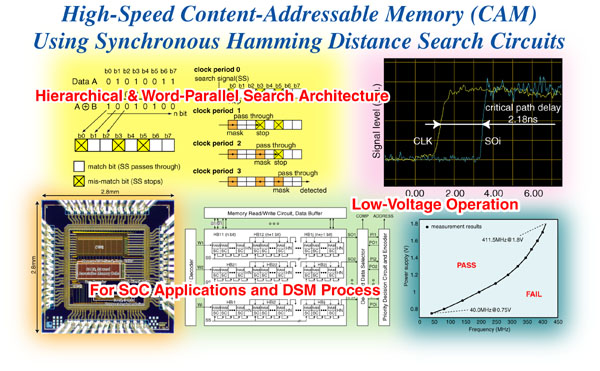

画像や音声に対する知的信号処理システム・認識システムなどの応用に

適用される、データ類似性を評価・検索する連想メモリの新しい方式を

検討しています。

従来、アナログ回路技術によって高速化が図られてきましたが、

私たちは今後の微細プロセスにおけるシステム・オン・チップとの整合性を

高めるために、ワード並列・階層探索構造によるハミング距離検索

アーキテクチャを提案しました。

本方式は、高速検索だけでなく、低電圧動作時も検索精度が保証され、

原理的に検索可能な容量に限界がありません。

最小距離検出だけでなく、全ての距離に対して検索が可能であり、

新しい応用の可能性があります。

本成果は、集積回路の会議としてISSCCに次ぐとされるCICCにて

2003年に発表しました。

Y. Oike, M. Ikeda, and K. Asada,

``A High-Speed and Low-Voltage Associative Co-Processor With

Exact Hamming/Manhattan-Distance Estimation

Using Word-Parallel and Hierarchical Search Architecture,''

IEEE Journal of Solid-State Circuits,

Vol. 39, No. 8, pp. 1383 -- 1387, Aug. 2004.

[PDF]

(This achievement was partly presented in

IEEE Custom Integrated Circuits Conf. (CICC), Sep. 2003.

[PDF])

Y. Oike, M. Ikeda, and K. Asada,

``Hierarchical Multi-Chip Architecture for High Capacity Scalability

of Fully Parallel Hamming-Distance Associative Memories,''

IEICE Trans. on Electronics,

Vol. E87-C, No. 11, pp. 1847 - 1855, Nov. 2004.

[PDF]

私たちは、さらに高度な認識処理を可能にするため、

より次元の高いマンハッタン距離でのデータ検索を

実現する検索アーキテクチャを検討しています。

Y. Oike, M. Ikeda, and K. Asada,

``A Word-Parallel Digital Associative Engine

with Wide Search Range Based on Manhattan Distance,''

in Proc. of IEEE Custom Integrated Circuits Conference (CICC),

pp. 295 -- 298, Oct. 2004.

[PDF]

![]()

Go Back...

Go Back...